|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Однокристальные микроконтроллеры

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 [ 17 ] 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

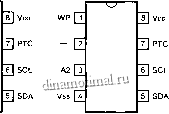

совместимы с чипами PCF8570, PCF8571, PCF8572 и PCF8581 по расположению выводов. Внутренее устройство микросхем PCF8582, PCF8594 и PCF8598 приведено на рис. 3.10.

Расположение выводов указанных микросхем приведено на рис. 3.11, назначение выводов - в табл. 3.3-3.5.

АО [Т

А1 [7 А2[Т Vss [7

Т\ Vdd WP [Т

Tj PTC AI [Т

7] SCL A2 [Т

J] SDA Vss [T

PCF8582

T7-

PCF8594

Рис. 3.11. Расположение выводов

PCF8598

Таблица 3.3. Назначение выводов PCF8582

Символ | Вывод | Описание |

Slave-адрес 0 | ||

Slave-адрес 1 | ||

Slave-адрес 2 | ||

Общий вывод | ||

Линия SDA вxovвыxoд | ||

Линия SCL вход | ||

Контроль времени программирования | ||

Вывод питания lt; + laquo; | ||

Таблица 3.4. Назначение выводов PCF8594 | ||

Символ | Вывод | Описание |

Защита записи | ||

Slave-адрес 1 | ||

Slave-адрес 2 | ||

Общий вывод | ||

Линия SDA вxovвыxoд | ||

Окончание таблицы 3.4

[j Символ | Вывод | Описание |

i: SCL | Линия SCL вход | |

! РТС | Контроль времени программирования | |

i %D | Вывод питания raquo;+ raquo; I | |

Таблица 3.5. Назначение выводов PCF8598 | ||

ji Символ | Вывод | Описание |

II WP | Защита записи j | |

Не используется | ||

1 А2 | Slave-адрес 2 | |

Общий вывод | ||

! SDA | Линия SDA вход/выход | |

;! SCL | Линия SCL вход ! | |

Контроль времени программирования | ||

Вывод питания | ||

Протокол программирования памяти микросхем аншюгичен приведенному ранее, но имеет некоторые особенности. Одна из особенностей связана с тем, что адрес ячейки памяти не может содержать число, превышающее 255. Но приведенигле типы лткросхем содержат 512 и 1024 ячейки. Что это означает? Вес очень просто: в : gt;1ауе-адресе биты Л0...А2 уже не все программируются внешними перемычками. Часть из них выбирается пporpaмню, при задании slave-адреса. Мы словно объединяем в одном корпусе несколько микросхем PCF8582. Структура памяти, состоящая из блоков по 256 байтов, называется страничной организацией. К слову, .макси.маль-ное чис.ю страниц в одной микросхеме 8.

Интересной возможностью, реализованной в описываемых микросхемах, является возможность защиты от повторной записи. Если вывод WP имеет низкий уровень, работа с EEPROM не имеет ограничений. Если WP устанавливается в состояние laquo;1 raquo;, верхняя половина памяти EEPROM заии1щается от записи. В таком случае сигнал АСК не будет генерироваться при адресации к верхней половине (256 байтов) PCF9594 и PCF8598 (512 байтов).

При записи данных в память EEPROM должны быть выдержаны определенные временные соотношения (циклы erase/write). Длительность этих циклов формируется внутри микросхс.\а gt;1 л в большинстве случаев не требует коррекции. Если коррекции не требуется, вывод РТС может быть подключен к V, или оставлен не подключенным. Типичное значение времени tp, = 7 мс, оно может быть задано внешне в пределах 4... 10 мс.

Как уже ранее было сказано, микросхемы EEPROM с последовательным доступом по ннгае PC выпускает не только фирма Philips, но и другие не менее известные фирмы. Для сравнения приведем описания микросхем 24LC16B и 24LC32A, производимых Microchip.

24LC16B

Емкость микросхемы - 16 кбитов, организованных в 8 блоков по 256 битов. Основные характеристики:

возможность питания пониженным напряжхчшем (до 2,5 В):

наличие входных формирователей (триггеров Шмитта) для обеспечения помехоустойчивости;

ток потребления в активном режиме 1 мА;

потребление в режиме ожидания - 10 мкА при питании 5,5 В и 5 мкА при питании 3,0 В;

организация 8 х 256 х 8 битов;

запита входов от потенгшального пробоя 4 кВ;

возможность работы в режиме fast-speed;

автоматическое выполнение цикла E/W;

внутренний буфер данных размером 16 байтов;

типичный цикл записи страиины данных - - 2 мс;

аппаратная защита от перезаписи;

гарантированное число циклов EfW - 1 ООО ООО;

сохранносгь записанных данных - не менее 200 (!) лет;

коммерческое (0...+70 deg;С) и индустриальное (-40...+85 deg;С) исполнения;

корпуса DIP и SOIC.

Расположение выводов показано на рис. 3.12.

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 [ 17 ] 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 |