|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 [ 149 ] 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

ров; оба эти выхода тоже равноправны. Таким образом, первый слой сумматоров как бы сворачивает т слагаемых, которые должны войти в окончательное произведение, в --т слагаемых.

Второй слой будет содержать-g-, т. е. -g-m рядов

одноразрядных сумматоров. Устроен он точно так же, как и первый слой. На каждый ряд одноразрядных сумматоров подадим 3 числа из выходных чисел первого слоя; на выходах этого ряда получим вместо тройки пару чисел.

Таким образом, во втором слое -д- т чисел свертываются в -j.T. е.

/ 2 ,

m .т. Q. в -тг гп чисел.

т

Далее в третьем слое поставим--,т. е.-27трядов

одноразрядных сумматоров, которые снова уменьшат количество имеющихся чисел в 1,5 раза и т. д. Только в самом конце, когда из т исходных чисел получится уже всего 2 числа, произведем суммирование этой пары чисел со всеми сквозными переносами; в результате и получим окончательный результат умножения.

Общее количество рядов одноразрядных сумматоров,

1 2

как нетрудно подсчитать, равно примерно-д-т.4--у-т--

4- 2 m -Ь .. . т, т. е. то же, что и в предыдущем многослойном построении. Однако количество слоев здесь несколько больше - log3 m (вместо logg/n в предыдущем построении).

Поэтому и время умножения несколько больше: вместо слагаемого log а/и Тв в него входит слагаемое logs/nTB. Зато

преимущество состоит в том, что в каждом слое (кроме последнего) все одноразрядные сумматоры срабатывают одновременно; распространение сигналов переноса от младших . разрядов к старшим внутри каждого слоя отсутствует. Это дает возможность строить схему из синхронных элементов, причем на каждый слой сумматоров нужно будет подавать

сигналы синхронизации в своей фазе: на первый слой - в одной фазе, на второй - с некоторым запаздыванием, на третий - с еще большим запаздыванием и т. д. Если к какому-то слою суммарное запаздывание составит целый период, так что на k-й слой сигналы синхронизации нужно будет подавать в той же фазе, что и на 1-й слой, то к-й и все последующие слои можно не строить; вместо этого выходные сигналы (к - 1)-го слоя можно подать на входы первого слоя (причем из сумматоров первого слоя будет использована только часть) и т. д.

В многослойных построениях, так же как в построениях разделов 4.5.1 и 4.5.2, сокращение количества оборудования и некоторое увеличение быстродействия могут быть достигнуты путем усложнения логики (см. 4.5.3).

4.6. 06 умноженки в последовательных устройствах

Многие из аппаратных методов ускорения умножения, рассмотренных нами ранее применительно к параллельным устройствам, могут быть в том или ином виде применены и при построении последовательных устройств. При этом, однако, большей частью сохраняется только общая идея; по форме же устройство получается совсем другим.

Ниже рассматриваются различные построения ускоренных множительных устройств последовательного типа. В части из них использованы те же рщеи, которые применялись для ускорения умножения в параллельных устройствах; другие основаны на отличных принципах.

Все изложение ведется применительно к двоичной системе, хотя многие из рассматриваемых построений можно непосредственно обобщить на любые другие основания системы счисления;

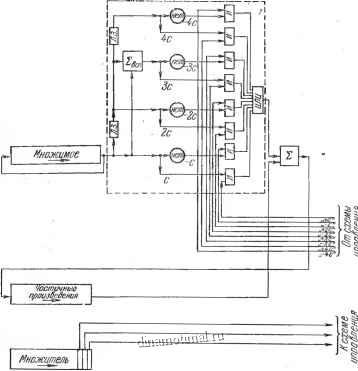

4.6.1. Использование чисел, кратных множимому. Использование чисел, кратных множимому, в последовательных устройствах по существу аналогично методу, описанному в разделе 4.4.1 применительно к параллельным устройствам. Конкретные решения могут быть весьма разнообразными. Одно из них - в качестве иллюстрации - приведено на рис. 4-13, причем технические подробности на рисунке опущены.

По сравнению с обычными множительными устройствами последовательного типа новым элементом здесь является схема формирования чисел, кратных множимому; на рисунке она обведена пунктирной рамкой. Непосредственно с выхода регистра множимого в последовательном коде

Рис. 4-13. Принцип построения последовательного множительного устройства, в котором для ускорения умножения используются числа, кратные множимому.

получаетсясамо множимое (с); инвертор ( laquo;нет raquo;), присоединенный к выходу регистра, позволяет одновременно получать обратный код множимого, т. е. величину -с (с учетом того, что в первом такте суммирования может быть

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 [ 149 ] 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |