|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 [ 49 ] 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

Второй полусумматор (на рис. 2-10 - справа) по тем же правилам суммирует цифру суммы двух слагаемых (3) с сигналом переноса в данный разряд (е). Если в первом полусумматоре сигнал переноса в следующий разряд не возник (Ej = 0), то он может возникнуть во втором полусумматоре - при условии, что одна из цифр слагаемых Ь или с равна единице (т. е. Р = 1) и имеется перенос в данный разряд (е = 1); если перенос в следующий разряд возник в первом полусумматоре (е = 1), то при этом Р = О и перенос во втором полусумматоре не может появиться. Окончательный сигнал переноса в следующий разряд ( ) должен передаваться в том случае, когда сигнал переноса возник либо на первом, либо на втором полусумматоре:

= -Ь е;

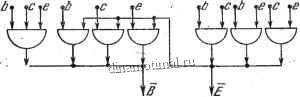

Рис. 2-11. Представление двоичного одноразрядного сумматора в виде двух полусумматоров.

сигнал суммы, появляющийся на выходе второго полусумматора, является, очевидно, суммой трех двоичных цифр {Ъ, с и е) по модулю 2, т. е. выходным сигналом двоичного одноразрядного сумматора {В). Построение сумматора рис. 2-10 было использовано в вычислительной машине laquo;Стрела raquo;.

На сокращенных функциональных схемах будем изображать полусумматоры в виде прямоугольников с буквой а внутри. Таким образом, полный одноразрядный сумматор рис. 2-10 может быть представлен так, как показано на рис. 2-11. Полусумматоры иногда называют сумматорами на два входа; при этом полный одноразрядный сумматор называется сумматором на три входа.

В ряде случаев полусумматоры используются в качестве самостоятельных функциональных устройств. При этом с целью унификации элементов машины каждый полный двоичный одноразрядный сумматор имеет смысл строить из двух полусумматоров. Но если отдельных полусумматоров требуется немного, то может оказаться, что по количеству оборудования (в частности, по количеству

инверторов) более экономно было бы принять в качестве унифицированного типового элемента полный одноразрядный сумматор; там, где требуется полусумматор, можно просто не задействовать один из его входов (присоединить к нему постоянно сигнал laquo;О raquo;).

Другое возможное построение полусумматора, требующее несколько большего количества диодов, чем на рис. 2-10, приведено на рис. 2-12 (схема, впервые примененная в машине EDVAC).

Вообще прямым перебором нетрудно показать, что построение полусумматора, приведенное на рис. 2-10, является наиболее экономным из всех возможных (6 диодов и 1 инвертор).

I Ш7и I

Рис. 2-12. Построение полусумматора вычислительной . машины EDVAC.

2.2.2. Использование других элементов. Сравнительные оценки, которые мы приводили в разделе 2.2.1, исходили в основном из количества оборудования, необходимого для реализации того или иного построения одноразрядного сумматора, причем подсчитывалось отдельно количество инверторов и отдельно количество диодов. Ясно, однако, что эти оценки весьма условны.

В качестве характерного примера рассмотрим применение элементов типа laquo;и-не raquo;. В последнее время появилось несколько разновидностей таких элементов, конструктивно оформленных в виде микромодулей. Первая логическая ступень элемента - laquo;и raquo; - может быть выполнена из сопротивлений, но чаще выполняется, как обычно, из диодов; существенно, однако, что выход этой первой ступени не может быть нигде использован непосредственно, поскольку он не выводится наружу из микромодуля, а соединен внутри со входом второй логической ступени - инвертора (обычно - полупроводниковый триод), в качестве выходного сигнала микромодуля используется выходной сигнал инвертора ( laquo;не raquo;), причем имеется возможность,

объединив общим проводом выходы нескольких инверторов, получить без дополнительных затрат оборудования вторую ступень laquo;и raquo;. Таким образом, типовая цепочка элементов имеет вид laquo;и-не-и raquo; либо просто laquo;и-не raquo; (если объединение выходов не используется).

С точки зрения логики цепочка laquo;и-не-и raquo; эквивалентна цепочке laquo;и-или-не raquo;, т. к. XjX...Xn = дг + -f ... -f x ; поэтому в принципе некоторые построения одноразрядных сумматоров, приведенные в разделе 2.2.1, могли бы быть повторены и на рассматриваемых элементах. Но при этом, если бы в качестве критерия для сравнения было выбрано по-прежнему количество оборудования, нас инте -ресовало бы только количество микромодулей. Сколько входов задействовано в первой ступени laquo;и raquo; и сколько выходов инверторов объединено между собой, не имеет значения, если только не превышены ограничения, которые задаются конкретно для каждой системы микромодулей. Если микромодуль, для примера, позволяет осуществить входную схему laquo;и raquo; на 3 входа, а мы используем laquo;и raquo; на 2 входа, то диоды неиспользуемых входов первой ступени laquo;и raquo; все равно остаются внутри микромодуля. Даже если схема laquo;и raquo; вообще не нужна, а нужен только инвертор, затраты оборудования не уменьшаются: на входе инвертора используется как бы схема laquo;и raquo; с одним входом, другие входы laquo;и raquo; не задействованы.

Рис. 2-13. Построение двоичного одноразрядного сумматора из элементов laquo;и-не raquo;.

На рис. 2-13 приведено одно из возможных построений двоичного комбинационного одноразрядного сумматора из элементов laquo;и-не raquo;, повторяющее в основном идею построения рис. 2-7,а на стр. 151. Элементы laquo;и.це raquo; обозначены полукругами; минимальное количествд рходов laquo;и raquo; в

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 [ 49 ] 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |