|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 [ 55 ] 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

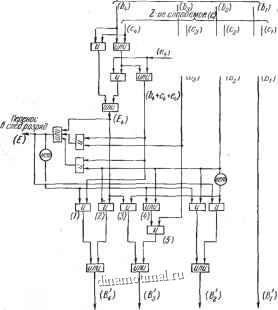

Схема рис. 2-19 скорее всего не является еще оптимальной с точки зрения количества оборудования. Получена она эмпирическим путем, и недостатком ее является значительно меньшая степень унификации отдельных частей, чем в схеме рис. 2-16.

I-Of. слагаемое (Ь)

/D /о , / , разряда (е)

й/тп (В)

Рис. 2-19, Десятичный одноразрядный сумматор комбинационного типа для кода laquo;8, 4, 2, 1 raquo;, в котором часть двоичных сумматоров заменена специальными логическими схемами.

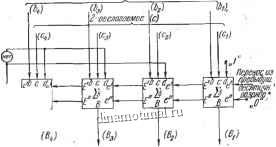

Если экономии в количестве оборудования не придается решающего значения, то можно построить схемы десятичных одноразрядных сумматоров с еще большей степенью унификации отдельных частей, чем, скажем, в схемах

рис. 2-16 или 2-17. Пример такого построения приведен на рис. 2-20 *).

Десятичный одноразрядный сумматор для кода с излишком 3, представленный на этом рисунке, состоит из чегырех одинаковых частей. Эти части изображены в виде прямоугольников со значком внутри. Каждая из них представляет собой двоичный одноразрядный сумматор на пять входов. Входы для пяти двоичных цифр обозначены

/-се слагаемое (Ь)

(Е) Не ucnoMTL

Сумма (в)

Рис. 2-20. Десятичный одноразрядный сумматор комбинационного типа для кода с излишком 3, выполненный из четырех двоичных сумматоров на 5 входов.

соответственно Ъ, с, d, е, е . Выходными переменными такого сумматора являются цифра суммы данного разряда (В) и две цифры переноса в следующий старший разряд (Л и ). Сумматор устроен так, что если все пять входных цифр равны нулю, то В = О и = = 0; если на одном из входов имеется единица, то В = 1, В = В = 0; если на двух из пяти входов имеются единицы, то В = О, а один из сигналов или Е равен единице; если на трех из пяти входов имеются единицы, то В = 1 и, один из сигналов Е или Е равен единице; если на четырех входах имеются единицы, то В = О, Л = Л = 1; наконец, при.

*) Идея схемы заимствована из работы Stone. Electronic Adder-accumulator (пат. США, кл. 235-61, № 2705108 от 29.03.1955 г.), хотя там речь идет не о комбинационном, а о накапливающем сумматоре.

наличии единиц на всех пяти входах должно получаться = = Е = К

В общем случае при., построении сумматора на 5 входов выходы Е и равноправны: если единицы имеются на двух или на трех входах, то в принципе все равно, где появится сигнал переноса - на выходе Е или на выходе Е . Однако для схемы рис. 2-20 существенно, чтобы наличие хотя бы двух единиц на входах Ь, с, е давало сигнал переноса на выходе Е, а наличие единиц на входах d и е вызывало бы появление сигнала переноса на выходе Е . Случаи использования сумматоров на 5 входов, где это не играет роли, имеются, например, в разделе 4.5.

В рассматриваемой схеме двоичные одноразрядные сумматоры на 5 входов используются так, что на входы Ьис подаются цифры двоичных представлений слагаемых, на вход е - сигнал переноса из предыдущего двоичного разряда, который может передаваться при сложении двоичных представлений слагаемых; Е есть сигнал переноса в следующий двоичный разряд, возникающий при суммировании в данном разряде цифр b и с с учетом е. На вход d подается цифра корректирующей поправки, а е и Е - это соответственно входной и выходной сигналы переноса, возникающие при выполнении коррекции.

Теперь ясно, что схема рис. 2-20 по существу ничем не отличается от схемы рис. 2-17. Каждую пару двоичных одноразрядных сумматоров на 3 входа, которые на рис. 2-17 изображены один под другим, соединенных так, как показано иа этом рисунке, можно представить в виде одного одноразрядного двоичного сумматора на 5 входов. Входы Ь, с и е верхнего одноразрядного сумматора на 3 входа будут являться соответственно входами Ь, с и е одноразрядного сумматора на 5 входов; входы сие нижнего одноразрядного сумматора на 3 входа являются соответственно входами d и е сумматора на 5 входов; выход В нижнего из пары сумматоров на 3 входа является выходом В сумматора на 5 входов, а выходы Е верхнего и нижнего сумматоров на 3 входа являются соответственно выходами Е и Е сумматора на 5 входов. Возможно, однако, что сумматор на 5 входов можно строить не из пары сумматоров на 3 входа, а каким-либо более экономным путем (подобно тому, как сумматор на 3 входа не обязательно строить

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 [ 55 ] 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |