|

www.chms.ru - вывоз мусора в Балашихе |

|

www.chms.ru - вывоз мусора в Балашихе |

Динамо-машины Обратные коды

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 [ 57 ] 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189

Q/Mimmp

1 \--

гашение

Разряд 10

smmm

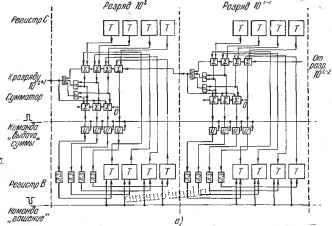

Рис. 2-22. Параллельный десятичный сумматор с числовыми регистрами: с) однотактный сумматор; б) двухтактный сумматор.

Так как за все время суммирования (от приема слагаемых в регистры до выдачи суммы) логические элементы сумматора срабатывают только по одному разу (напряжения на их входах не изменяются), сумматор рис. 2-22, а называется однотактным.

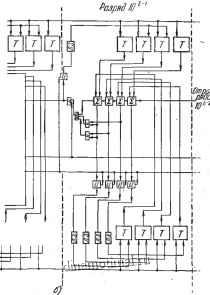

На рис. 2-22,6 показаны те же два регистра - В и С - и сумматор, но сумматор здесь двухтактный.

Внешне схема отличается главным образом тем, что в каждом из десятичных разрядов отсутствуют нижние ряды одноразрядных двоичных сумматоров, которые в схеме рис. 2-22,0: служат для добавления корректирующей поправки. Оставшиеся верхние ряды сначала производят в каждой тетраде сложение цифр слагаемых по правилам двоичной арифметики, а потом - коррекцию результата.

В первом такте в регистрах В и С находятся исходные слагаемые. Складывая внутри каждой тетрады изображения десятичных цифр по правилам двоичной арифметики, сумматор в то же время формирует переносы из тетрады в тетраду по правилам десятичной арифметики. Цепь образования переносов здесь такая же, как на рис. 2-22, а; в каждом разряде имеется дополнительный элемент laquo;и raquo;, который позволяет прервать образование сигналов переноса, подав запрещающий уровень напряжения на шину laquo;разрешение переноса raquo;. Однако в течение первого такта схема управления удерживает на этой шине разрешающее напряжение.

Затем, точно так же как в схеме рис. 2-22, а, произво- дится вьщача суммы в регистр В (но при этом выдается не-корректированная сумма). Одновременно в регистр С выдаются корректирующие поправки, где они заменяют другое слагаемое. Для этого в каждом десятичном разряде имеется дополнительный элемент laquo;и raquo;, который пропускает импульс laquo;вьщача суммы raquo; в том случае, если из данного десятичного разряда имеется перенос в следующий десятичный разряд, и устанавливает в laquo;1 raquo; 2-й и 3-й триггеры данной тетрады (т. е. ставит в ней число 6).

Во втором такте некорректированная сумма, находящаяся в регистре В, складывается с корректирующими поправками из регистра С. Цепь десятичных переносов при этом должна быть закрыта (запрещающий уровень на шине laquo;разрешение переноса raquo;). Правильная сумма затем

прежним путем передается в регистр В. Одновременно с гашением В вновь устанавливается в laquo;О raquo; регистр С; но теперь дополнительные элементы laquo;и raquo; ни в одном из разрядов не дают сигналов (так как десятичные переносы отсутствуют), и в регистр С ничего больше не принимается.

Сумматор на рис. 2-22,6 требует почти вдвое меньше оборудования, чем сумматор на рис. 2-22,й. Но и време- ни для выполнения сложения требуется примерно вдвое больше, так как и логические элементы в сумматоре должны сработать по два раза и дважды должен произойти прием в регистр В. Впрочем, временные соотношения сильно зависят от того, какую роль играют различные компоненты в общем времени выполнения сложения. Например, если основную роль играет время установления сигналов десятичного переноса, то второй такт может быть существенно короче, чем первый, так как во втором такте десятичные переносы отсутствуют.

Рис. 2-23 иллюстрирует другой принцип построения многотактного десятичного сумматора. На этом рисунке представлен последовательный десятичный сумматор для кода с излишком 3. Нри этом предполагается, что не только десятичные цифры поступают в сумматор последовательно, но и все двоичные разряды, которые составляют изображение одной десятичной цифры, поступают последовательно, один за другим, по одному и тому же проводу, с периодом тактовой частоты т.

Если бы двоичные цифры, которые относятся к одному десятичному разряду, поступали в сумматор одновременно (по 4 разным проводам), то полная схема сумматора должна была бы состоять из одноразрядного десятичного сумматора, выполненного, например, в соответствии с рис. 2-17, и элемента задержки на 1 такт - для запоминания цифры переноса в следующий десятичный разряд (см. рис. 2-2). Такой сумматор мы называли бы однотактным, так как суммирование одной пары десятичных цифр выполнялось бы в нем в течение одного такта. Нри этом, как видно из рис. 2-17, схема содержала бы 8 одноразрядных двоичных сумматоров.

В схеме рис 2-23 имеется всего 2 одноразрядных двоичных сумматора - в четыре раза меньше. Зато

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 [ 57 ] 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 |